These devices conform to all s in the I2CTM 2-wire protocol and are designed to minimize device pin count, and simplify PC board layout requirements. The NM24C04/05 devices are 4096 bits of CMOS non-volatile electrically erasable memory. Package = 5.0 X 7.0 X 2.0 MM Frequency = 12.600 to 19.800 MHZ Output Logic = Clipped Siave Supply Voltage = 3.0 Volt. Acceleration: Device unclamped Device clamped DS Da Weight. Optimized for high current rectifiers Very low on-state voltage Very low thermal resistance VRRM VRSM IRRM Repetitive peak reverse voltage Maximum peak reverse voltage Repetitive peak reverse current 50 mA Half sine wave, = 10 ms, 50 Hz Half sine wave, VR = VRRM FM a Mounting force min. H5A32C3 : Um-1, Um-4, UM-5 Microprocessor CrystalĬFPO-DO-340C12A50N : Range of Super Single Oven Ocxo¡¯sĥSDD40B0200. 100 Contact Centers, 431 Insulator Height LSMH-1005-4N7S-B : High Frequency Multilayer Chip InductorĮZC50HRTF. SLBSC1 2.0mm Ceramic Surface Mount Crystalġ140-G211-P1M1-12A : Thermal Overcurrent Circuit Breaker 025(0.64mm) Square Postsġ206X104XXX Ceramic Multilayer Capacitors RDPS-POTS050 Micro Filter for South AfricaĢN711A Silicon Transistors Uhf/vhf Power Transistors MTB10HF Full-size (7.3mm or 4.7mm Height) UT300020 Diffuse Reflection Sensor (analogue/digital)

TTC-8100 10/100 Base- T LAN Magnetic Module Single Port, 16 pin SOIC GF063P1K 1/4 Square, Single-turn, Through-hole Sealed Cermet Trimmers 025(0.64mm) Square PostsġN4613C Temperature Compensated Zener Reference DiodesĪU6331 Usb2.0 Sd/mmc/ms Single/dual LUN Card Reader Controller Q元012-0PQ208M 60,000 Usable PLD Gate Pasic3 FPGA Combining High Performance and High Density Some Part number from the same manufacture ETC The QuickWorksTM-Lite and QuickToolsTM packages provide a solution for designers who use Cadence, Exemplar, Mentor, Synopsys, Synplicity, Viewlogic, Veribest, or other third-party tools for design entry, synthesis, or simulation.

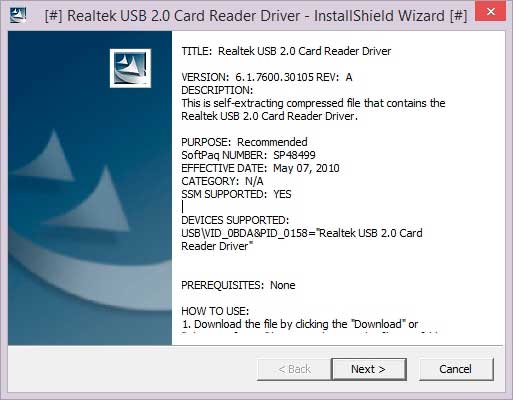

AU6331 DRIVER FOR MAC SOFTWARE

The turnkey QuickWorks® package provides the most complete FPGA software solution from design entry to logic synthesis, to place and route, to simulation. Software support for the complete pASIC 3 family is available through three basic packages. With a maximum of 316 I/Os, and is available in 208-PQFP and 84-PLCC packages. The pASIC 3 product family contains 1,584 logic cells. pASIC 3 FPGAs are fabricated a 0.35mm four-layer metal process using QuickLogic's patented ViaLink technology to provide a unique combination of high performance, high density, low cost, and extreme ease-of-use. The pASIC 3 FPGA family features to 60,000 usable PLD gates. Input + logic cell + output total delays under 6 ns Data path speeds exceeding 400 MHz Counter speeds over 300 MHz

AU6331 DRIVER FOR MAC FULL

Interfaces with both 3.3 volt and 5.0 volt devices PCI compliant with 3.3V and 5.0V buses for -1/-2 speed grades Full JTAG boundary scan Registered I/O cells with individually controlled clocks and output enables Two array clock/control networks available to the logic cell flip-flop clock, set and reset inputs - each driven by an input-only pin Up to six global clock/control networks available to the logic cell F1, clock, set and reset inputs and the input and I/O register clock, reset and enable inputs as well as the output enable control - each driven by an input-only or I/O pin, or any logic cell output or I/O cell feedback 60,000 Usable PLD Gate pASIC3 FPGA Combining High Performance and High DensityĦ0,000 Usable PLD Gates with 316 I/Os 16-bit counter speeds over 300 MHZ, data path speeds over 400 MHz 0.35um four-layer metal non-volatile CMOS process for smallest die sizesģ08 bidirectional input/output pins, PCI-compliant for 5.0 volt and 3.3 volt buses for -1/-2 speed grades 8 high-drive input/distributed network pinsġ00% routable with 100% utilization and complete pin-out stability Variable-grain logic cells provide high performance and 100% utilization Comprehensive design tools include high quality Verilog/VHDL synthesis